Other products

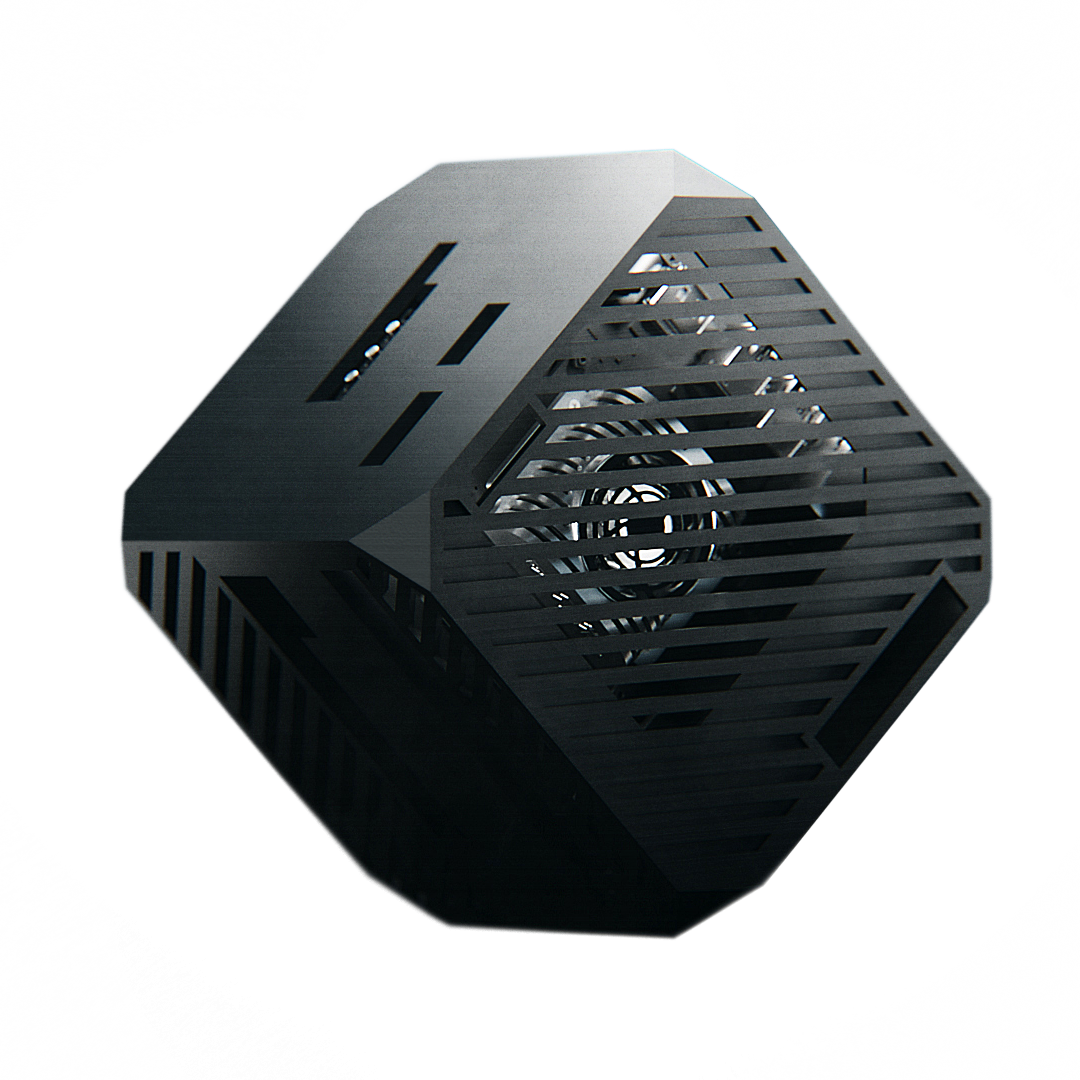

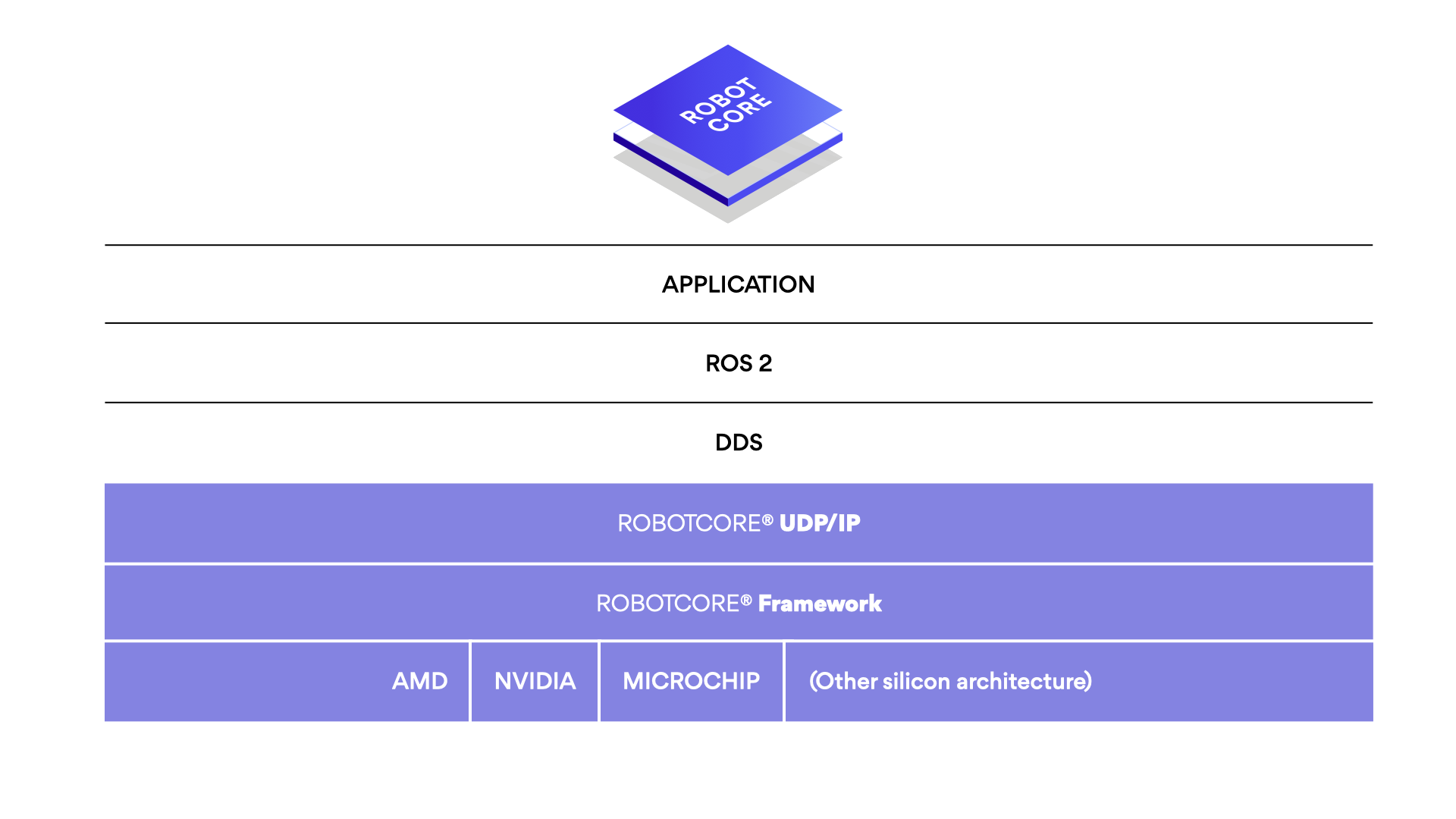

ROBOTCORE UDP/IP

FPGA UDP/IP Networking Stack to push Robots to Nanosecond Speeds

ROBOTCORE® UDP/IP is an innovative FPGA robot core (also known as IP core), specifically engineered to significantly enhance the efficiency and speed of Internet Protocol (IP) networking stack communications utilizing the User Datagram Protocol (UDP). Designed with the cutting-edge demands of robotics and high-speed communication systems in mind, ROBOTCORE® UDP/IP can send or receive small packages in 700 nanoseconds, accelerating networking by more than 19x when compared to traditional CPUs. A pivotal component in modern real-time and fast networking robotic infrastructures.

Get ROBOTCORE® UDP/IP Benchmarks